放置してたZYBOで遊んでみる

買ったはいいけど全然使っていなかったZYBO。せっかくなのでブログのネタとしてプロジェクトを作ってLEDとか光らせてみたいと思う。いわゆるLチカ。最終的にはARMのプロセッサを含むブロック(PS)も含めて使うことになると思うけど、まずは純粋なFPGAのロジックブロック(PL)だけを使ってみたいと思う。

環境

Windows10

Vivado 2016.2

ZYBO

プロジェクトの作成

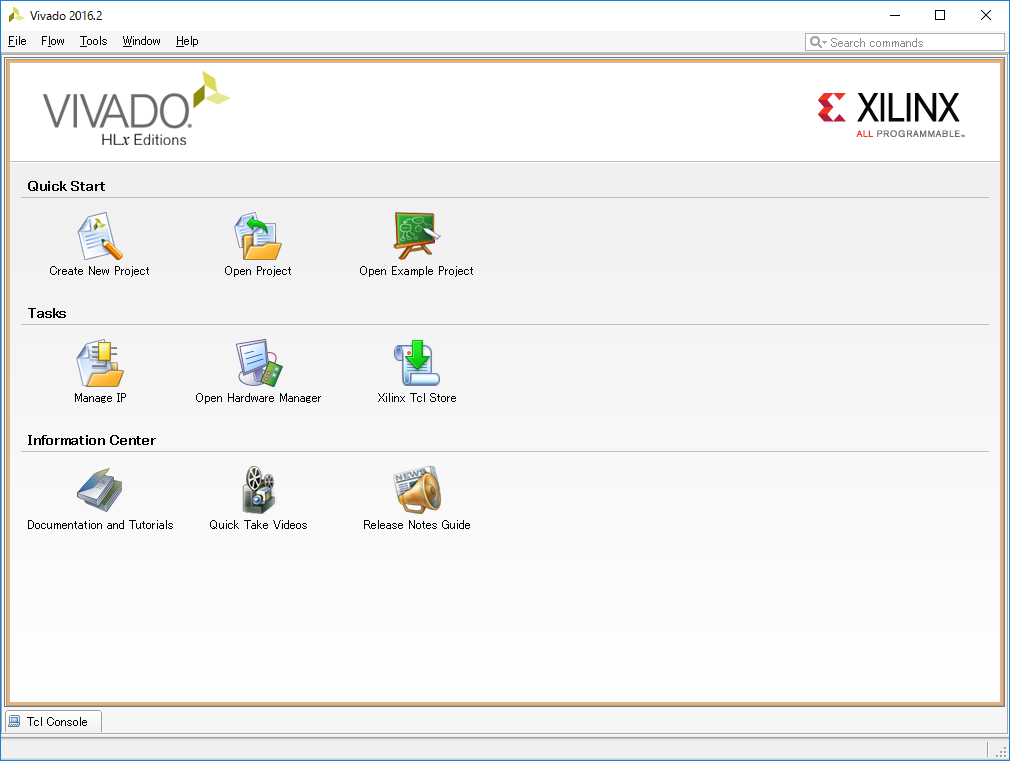

今回は初歩の初歩ということで、プロジェクトの作成から。まず、Vivado 2016.2を起動し、Create New Projectをクリック。

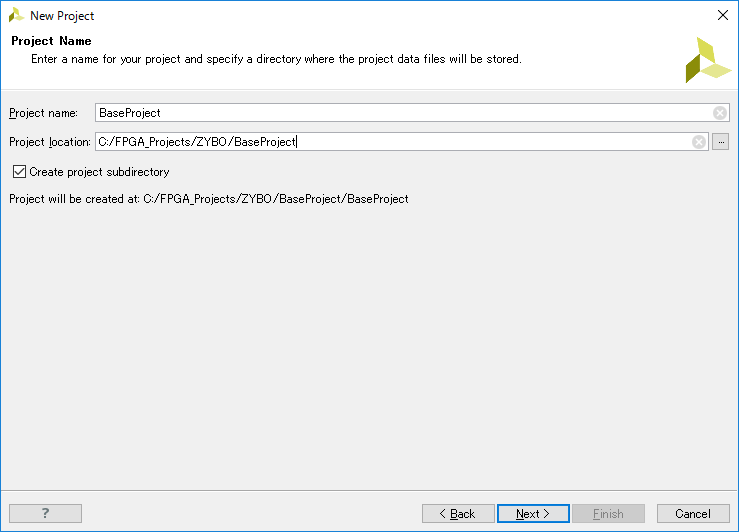

最初の画面で「Next」を押し、以下のようにプロジェクト名とプロジェクトを作成する場所を選ぶ。このプロジェクトをベースにして色々つくっていくつもりなので、とりあえずBaseProjectという名前にした。

Nextを押すと、以下の画面になる。

Example Projectを改造するのもありだけどGithubとかにも上げたいし、今回は自分で一から作ることにする。ということでRTL Projectを選択。まだRTLや制約ファイルはつくってないので、「Do not specify sources at this time」にチェックをして、とりあえずプロジェクトだけ先につくる。Nextを押すと、プロジェクトを作る対象のFPGAを選択する画面になる。

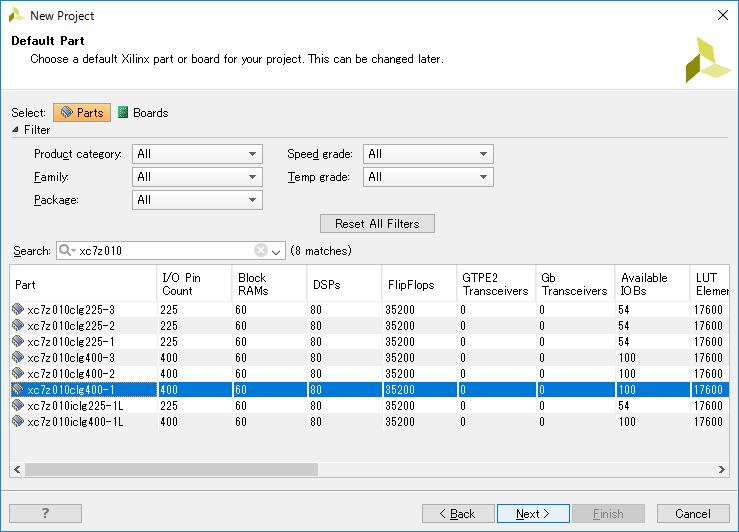

デバイスの選択

Searchにxc7z010とか入れれば絞り込んで検索できる。Zynq XC7Z2010-1CLG400CがZYBOのFPGAのデバイス名。xc7z010clg400までは直感的にわかりそうだけど、FPGA慣れない人はそのあとの-1とか-2とか-1Lって何?と思うかもしれない。これはスピードグレードを表していて、簡単に言えば数字が大きいほど高い周波数の信号を扱うことができる。

ZYBOの場合はxc7z010clg400-1が正しい。デバイス名の命名則は以下の資料の23ページあたりに書いてある。

http://japan.xilinx.com/support/documentation/data_sheets/j_ds190-Zynq-7000-Overview.pdf

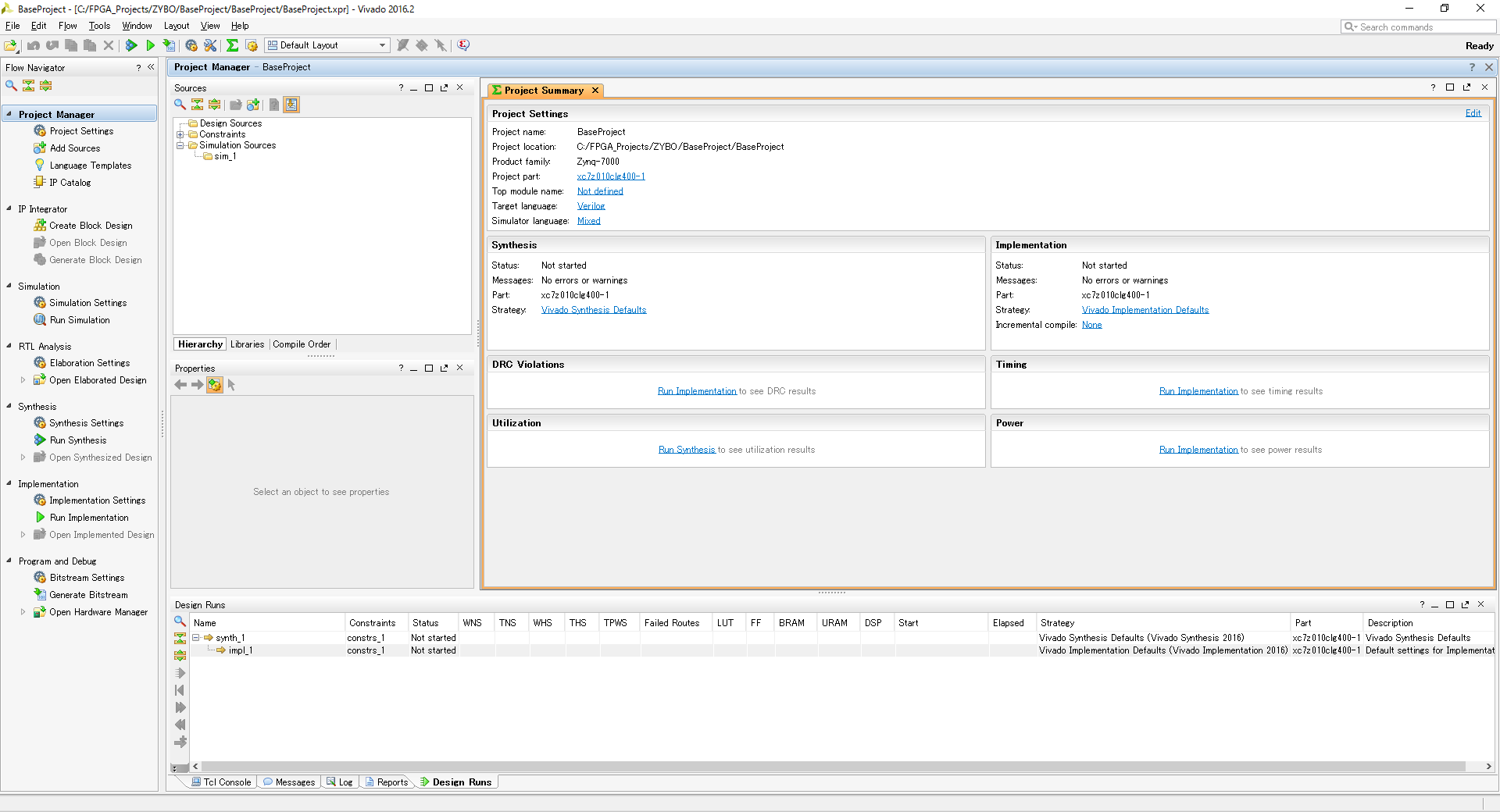

デバイスを選択してNextをクリックし、次の画面でFinishをクリックすればプロジェクトの作成は完了。プロジェクトが作成させると、以下のように表示されるはず。

次回はトップモジュールのRTLを書いていきたい。

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/