今回やること

前回、ZYBO用のプロジェクトの作成まで行った。今回は、トップモジュールのRTLを書いてみる。

ZYBOの入門ではARMを含むPSブロックを使って、「Hello World」からやるパターンが多いみたい。それもいずれやるつもりだけど、今回はあえてZYBOのPLブロックを使い、RTLを書いてハード的にいじっていきたいと思う。とりあえずはLEDを光らせることを第一目標として進める。(※備忘録的に書いていくつもりなので、あまり丁寧ではないかもしれないのでご了承ください)

環境

Windows 10

Vivado 2016.2

ZYBO

回路図の確認とRTL作成

とりあえず最低限LEDだけ光らせるためには、クロックとLEDのIOをトップモジュールに追加すればいい。IOを追加する前に、クロック、LEDの接続を回路図を確認してアタリを付けておく。回路図は秋月電子で「ZYBO」と検索すれば載っている。また、同じページにあるマニュアルを参照すると、21ページ目にクロックソースに関する記載がある。L16ピンのSYS_CLKについて、

「 which can be useful for simple applications that do not require the processor」

とある。今回はプロセッサは使わないので、このクロックで動かしてみる。あと、のちのちのデバッグ用にロジカルなリセットも欲しい。といわけで適当にR18ピンのBTN0を使おう。(※マニュアル24ページにあるボードとしてのリセットではなく、作成したRTLの回路を初期化するためのリセットなので注意)LEDは4つあるようなので、4bitで定義する。というわけで以下のようにverilogでトップモジュールをつくった。

クロックの周波数は125MHzなので、1秒ごとにLEDを点滅させるためのカウンターをつくっている。LEDはビット反転で4つ同時に点滅するようにした。

Verilogコードをプロジェクトに追加する

次はソースコードをプロジェクトに追加する。以下の「Add Sources」からソースコードを追加。

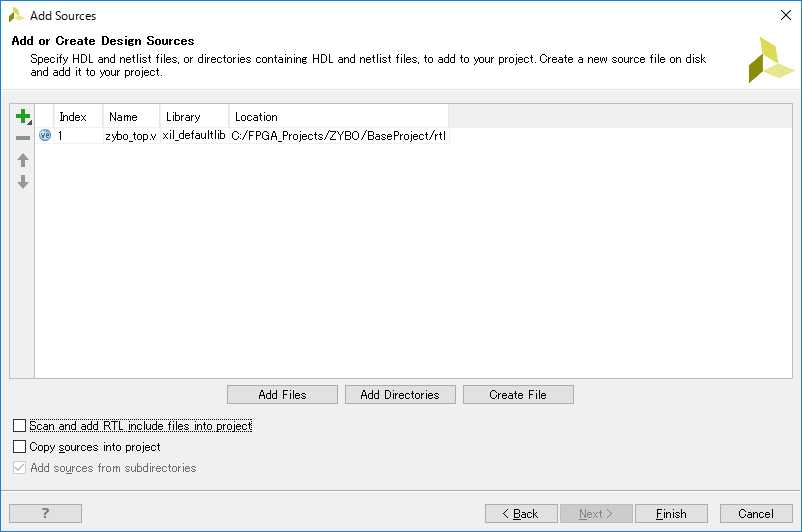

ウィンドウが出たら、「Add or create design sources」を選択。そして「Add Files」で先ほどのソースを選択して「Finish」でソースコードを追加。

RTLを合成

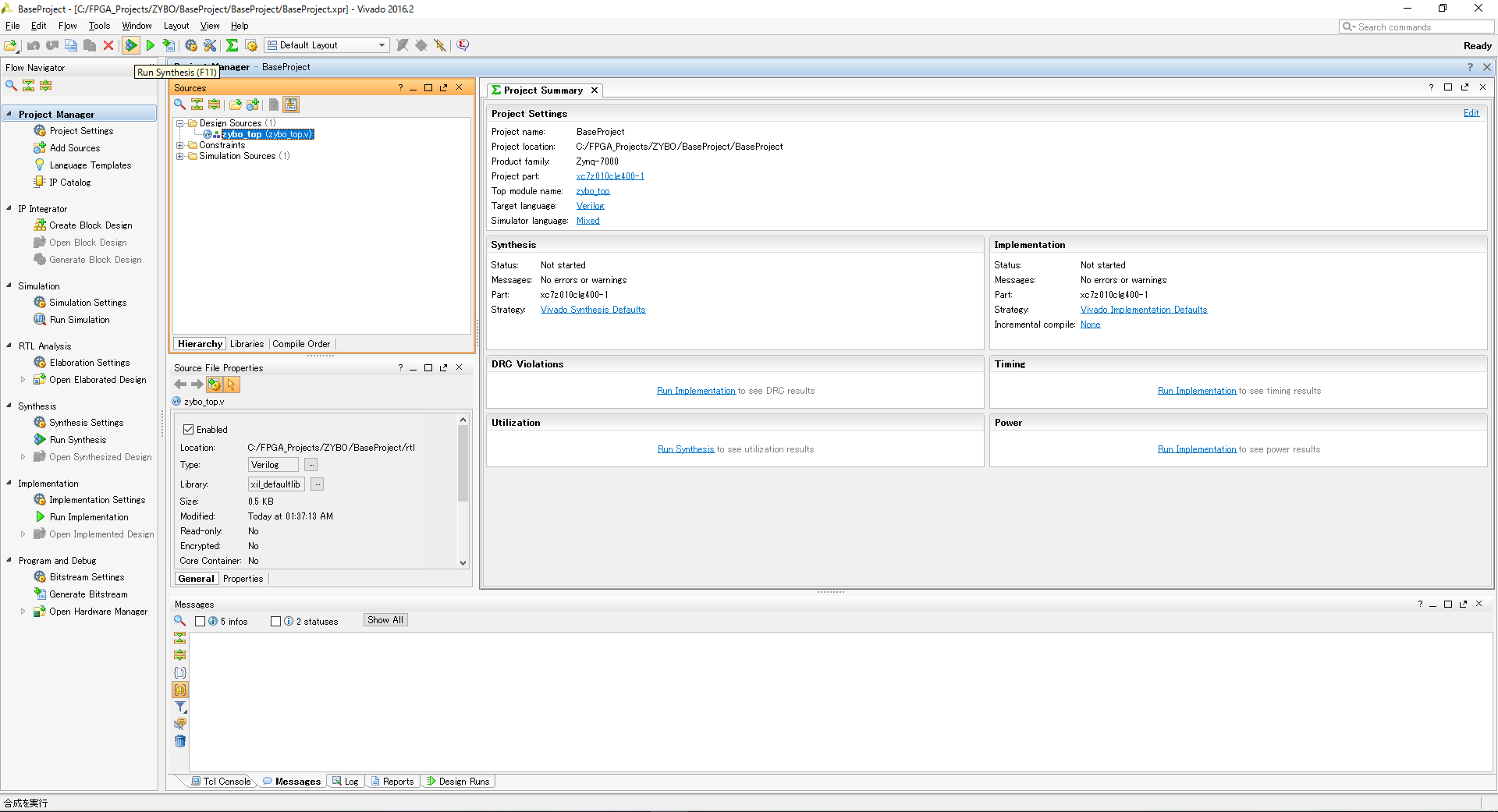

以下のようにプロジェクトにソースコードが追加されるので「Run Synthesis」で合成する。

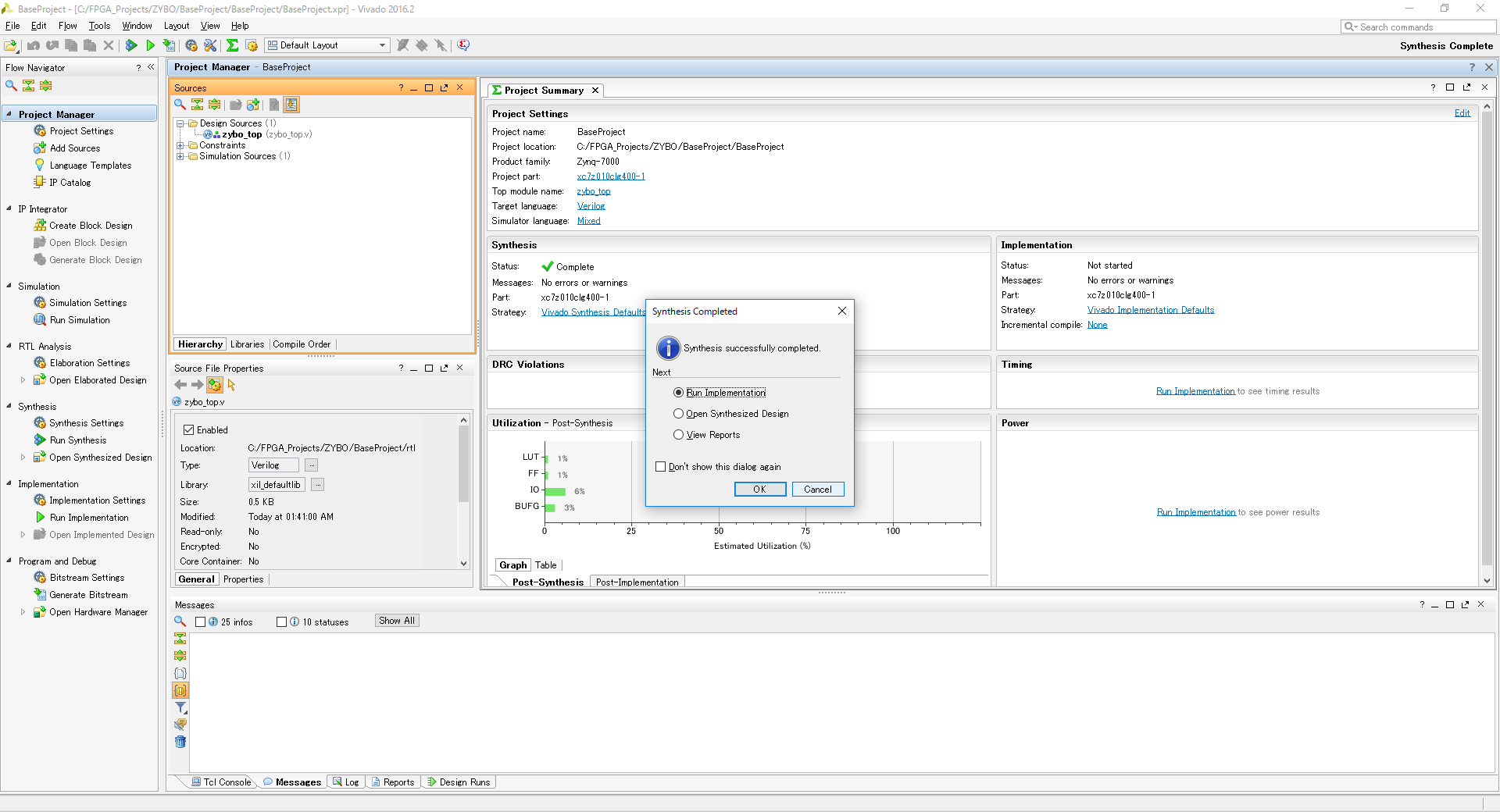

合成後、CLK、RST、LEDのピンアサインを設定するため、出てくるメニューで「Open synthesized design」を選択する。

ピン配置を設定

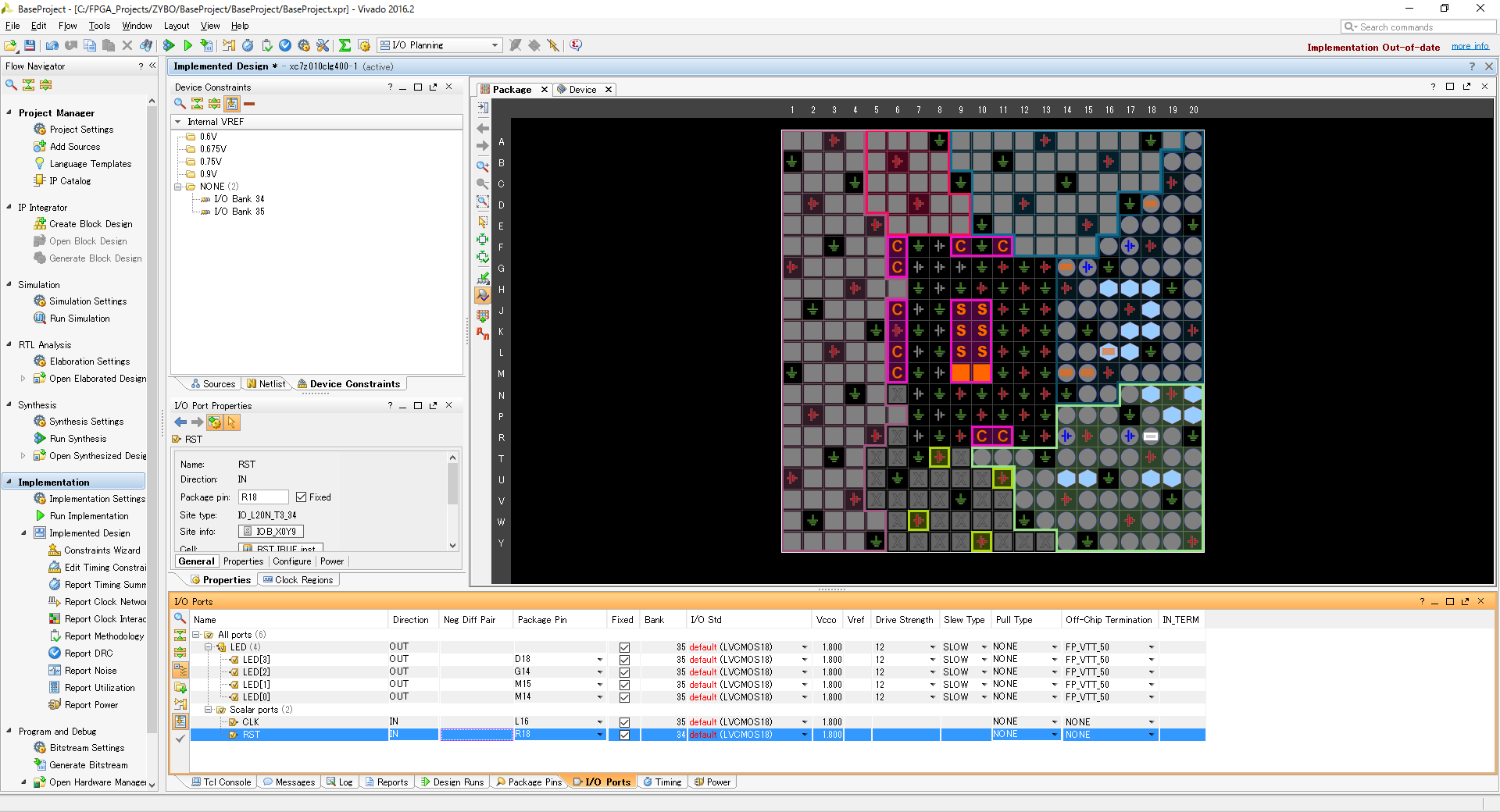

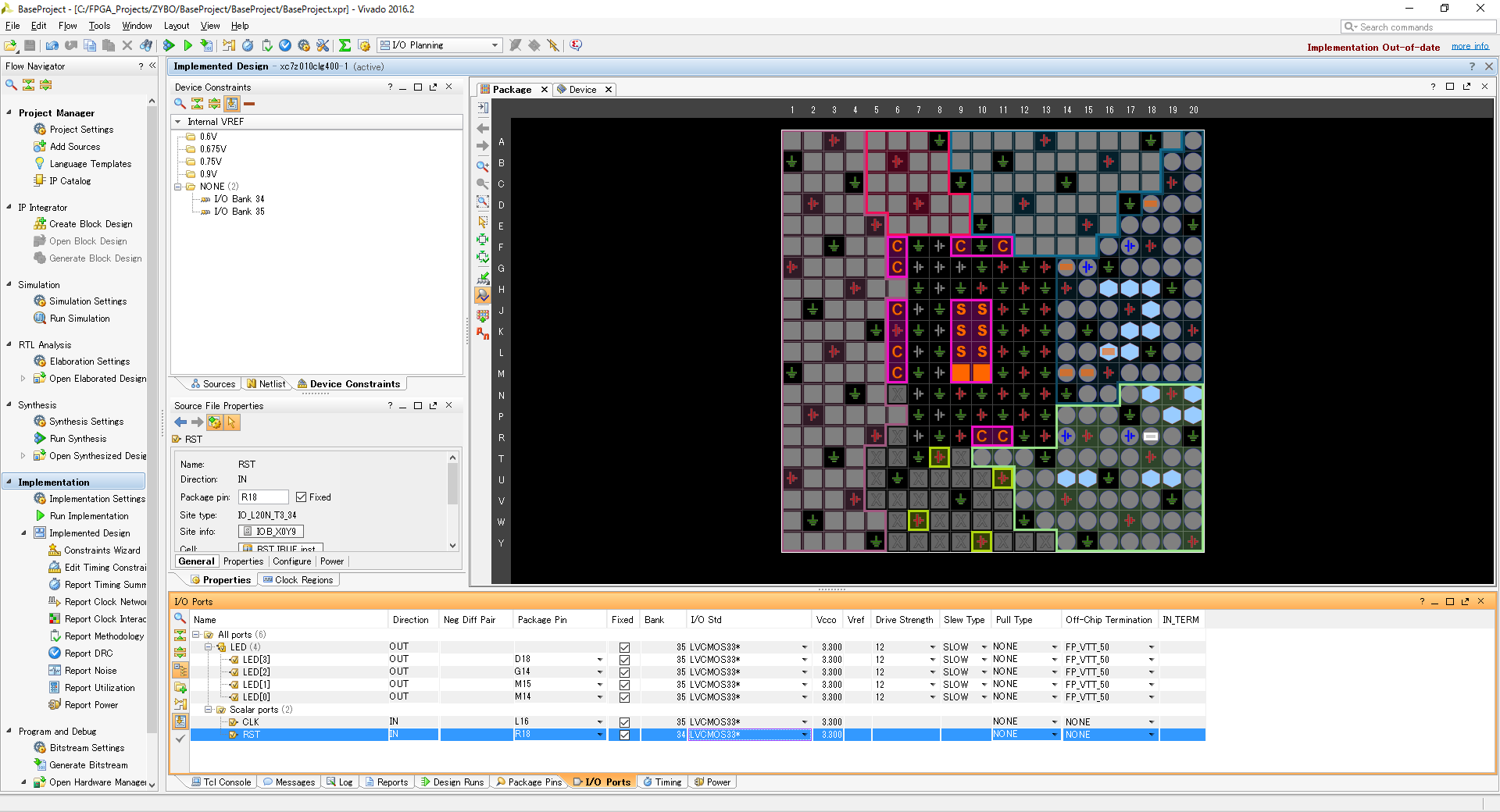

ここで「Window」から「I/O Ports」を選択してI/Oピンを設定する。以下のような画面が出るので、回路図を見ながら「Package Pin」でピンロケーションを設定する。

そして、「File」から「Save constraints」を選択。Out of Data Designというウィンドウが立ち上がるけど、要約するともう一回合成してねということなので「OK」を選択。ここで入力したピンアサインは、XDCという形式の制約ファイルとして保存される。制約ファイルというのはピンアサインや信号の入出力のタイミングを規定するファイル。今回は上のようにGUIで設定したけど、大規模なデバイスになるとXDCファイルを直書きした方が早かったりする。

※追記

結構大事なことを書いていなかったので追記。

今回は125MHzのクロックを使うのだが、インプリテーションをするにあたって設計ツールにクロックの周波数を教えてあげないと後々問題が起こる(たとえばLogic Analyzerという機能でFPGA内の信号を観測するときなど)。上記のピンアサインをすると拡張子.xdcファイルが生成されるはずなので、以下の分を追加する。

create_clock -period 8.000 -name sys_clk_pin -waveform {0.000 4.000} -add [get_ports CLK]

periodというのはnsec単位で書くクロック周期で(1sec/125MHz=8nsec)、waveformの後の数字はクロックの位相を規定している。

インプリテーションの実行

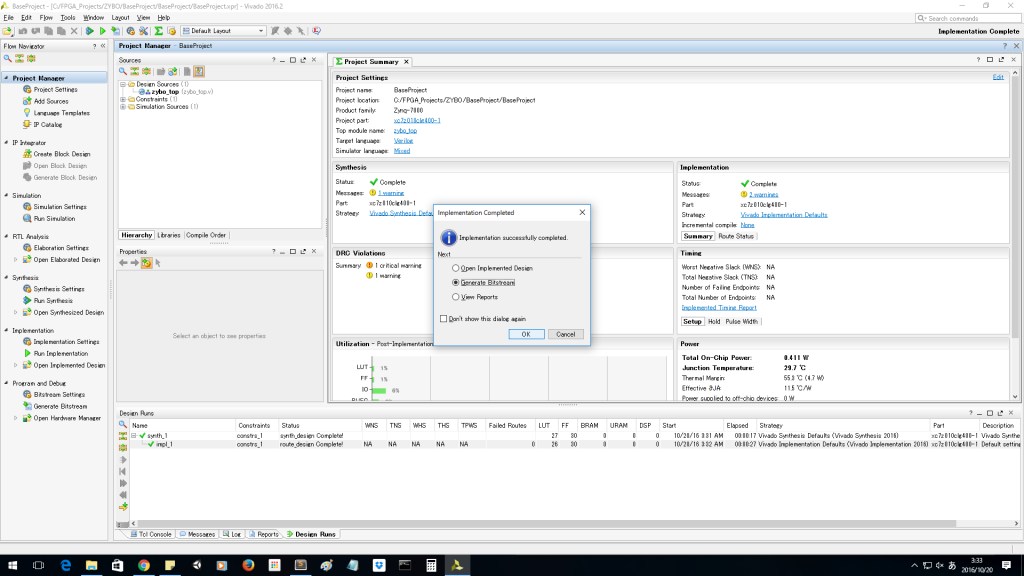

適当に名前を付けて、制約ファイルを保存。Synthesized Designを閉じ、「Run Implimentation」を選択。合成しますか?というようなメッセージが出てくるのでOKを押す。エラーなしで成功すると以下のような画面が出てくる。

これでOKかと思いきや……

JTAG経由で書き込む.bitファイルを作るために「Generate Bitstream」を選択してOK。これで準備完了・・・のはずだったが以下のようなエラーが。

[DRC 23-20] Rule violation (NSTD-1) Unspecified I/O Standard – 6 out of 6 logical ports use I/O standard (IOSTANDARD) value ‘DEFAULT’, instead of a user assigned specific value. This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards. This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined. To allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: LED[3:0], CLK, RST.

ピンアサインのときにI/O StandardをDEFAULTにしているとだめらしい。というか回路図とマニュアル見ると、CLOCKとFPGA IOは3.3Vになってた。危ない危ない。ということで以下のようにI/OLVCMOS33に設定しなおして保存。

この状態で「Run Implimentation」し、「Generate Bitstream」すると無事に成功した。デフォルトだと生成されたbitファイルは「impl_1」というフォルダに含まれている。次回はいよいよZYBOのLEDを光らせてみる。

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/